Free Webinar – Real Number Modeling with System Verilog

Real Number Modeling with System Verilog – Course Duration

Real Number Modeling – 3 Days (8 hours per Day)

Real Number Modeling with System Verilog – Abstracts

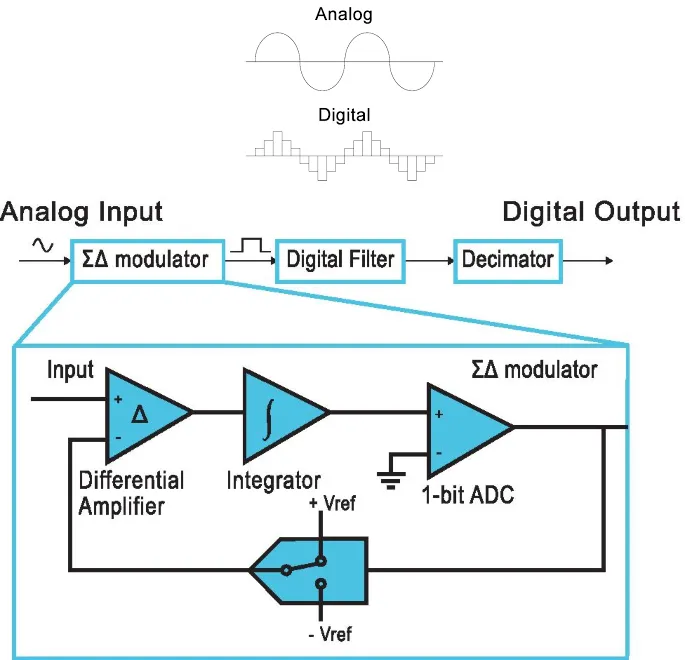

Nowadays, the semiconductor industry directs its attention to mixed-signal System-on-Chip (SoC) applications. Main targets are the creation of accurate and fast mixed-signal SoC designs, composed of both digital and analog components, and the reduction of time to market for this kind of integrated circuits (ICs). In order to bring a mixed-signal SoC faster to the market, higher system-level simulation speed is required, with respect to traditional modeling approaches. Real Number Modelling (RNM) could be an effective solution. In this work, a sigma-delta analog-to-digital converter (ADC), a voltage-controlled oscillator (VCO) and a digital phase-locked loop (PLL) are implemented as real number models using System Verilog. This paper is an extended version of work previously published by the authors. Herein, more accurate and parameterizable models were created, while their validation process is analyzed and achieved using a novel metric for accuracy estimation. The proposed models’ parameterizability enhances the usability of the models to various SoC designs. Aim of this work is to underline the RNM effectiveness provided by SystemVerilog, and exhibit a way to apply RNM for modeling and simulation of widely used analog/mixed-signal (AMS) blocks. The presented real number models were compared to Verilog-A, Verilog-AMS, and transistor-level SPICE models. All tests showed that the proposed real number models based on SystemVerilog demonstrate noteworthy improvement on simulation efficiency, with respect to previous works in the literature, preserving simultaneously sufficient accuracy.

Course Description

In this course, you focus on Real-Number Modeling (RNM) using the SystemVerilog language in a mixed approach, borrowing concepts from the digital and analog domains to enable high-performance, digital-centric, mixed-signal verification.

In the course, you learn how to model analog block operation as discrete real data to improve top-level verification performance using SV real data type and nettypes. It stresses SystemVerilog 2012 Extended Nettype Capabilities (built-in, UDT/UDR) and Interconnects. You learn to use the Cadence® package “EE_pkg” that defines nettype “EEnet” to describe analog impedance-based interactions between blocks in a SystemVerilog DMS environment. You then examine advanced RNM features, SV port connections, and Connect Modules (CM) for AMS interactions. The nettype debug and performance improvement are discussed. Most of the labs in this course are in command-line mode using the Xcelium™ simulator with the mixed-signal option. In addition to that, you work with System Verilog Models and Packages in the Virtuoso® environment.

Learning Objectives

After completing this course, you will be able to:

1. Identify how Real-Number Modeling (RNM) using System Verilog enables high-performance digital-centric, mixed-signal SoC verification

2. Create real-number models with System Verilog real variables and nettypes

3. Apply the real modeling techniques for creating analog operations and functions

4. Identify System Verilog 2012 Extended Nettype Capabilities (built-in, UDT/UDR) and Interconnects

5. Examine the Cadence package “EE_pkg” that defines nettype “EEnet” for electrical pin modeling

5. Explore advanced SVRNM features and Connect Modules (CM) for AMS interactions

6. Identify how SV port connections are resolved in mixed designs using wildcard (.*) notation

7. Debug the Nettype (UDT/UDR) struct values using Tcl commands and system functions

8. Improve performance with incremental elaboration at the SVRNM partition boundary

Software Used in This Course

1. Xcelium Digital Mixed-Signal App

2. Xcelium Single Core

3. Xcelium Limited Single Core

4. SimVision Waveform Display

5. Spectre AMS Designer

6. Spectre AMS Connector

7. Spectre Multi-Mode Simulation with AMS

8. Virtuoso Schematic Editor

9. Virtuoso Simulation Environment

10. Virtuoso ADE Explorer and Assembler

11. Virtuoso Visualization & Analysis

Modules Available in Real Number Modeling Course

1. Introduction to Real Modeling

2. SVRNM Basics

3. SV Real Modeling Techniques

4. Advanced SVRNM Modeling Techniques

5. Modeling Electrical Circuits Using Cadence “EE_pkg”

6. SVRNM Capabilities and Interactions

7. SVRNM Debug and Performance Improvement

8. Optional Appendices

9. SV-RNM in the Virtuoso Environment

10. System Verilog Basics

11. SV Real Number Modeling Examples

Audience

Verification engineers, verification leads, designers, and managers interested in improving the predictability, productivity, and quality of mixed-signal SoC verification runs

Analog and mixed-signal SoC verification engineers looking to learn about event-based behavioral modeling techniques

Digital and SoC verification engineers looking to achieve >100X to 500X performance improvements in their nightly regression runs

Prerequisites for Real Number Modeling

You must have a working knowledge of Verilog and SystemVerilog languages and experience working with the AMS Designer simulator, and have completed the following courses:

1. SystemVerilog for Design and Verification

2. Mixed-Signal Simulations Using Spectre AMS Designer

3. Command-Line Based Mixed-Signal Simulations with the Xcelium Use Model

How to Register

If you don’t have a account with Silicon Synergy Registration, fill out the below form and complete the requested information to enroll and hit on ‘Submit’ button.

Related Courses – Coming Soon

SystemVerilog for Design and Verification

Mixed-Signal Simulations Using Spectre AMS Designer

Command-Line Based Mixed-Signal Simulations with the Xcelium Use Model

Real Modeling with Verilog-AMS

Please see course learning maps at this link for a visual representation of courses and course relationships.