Protected: Introduction to CAD of Integrated Circuits – UCB

There is no excerpt because this is a protected post.

There is no excerpt because this is a protected post.

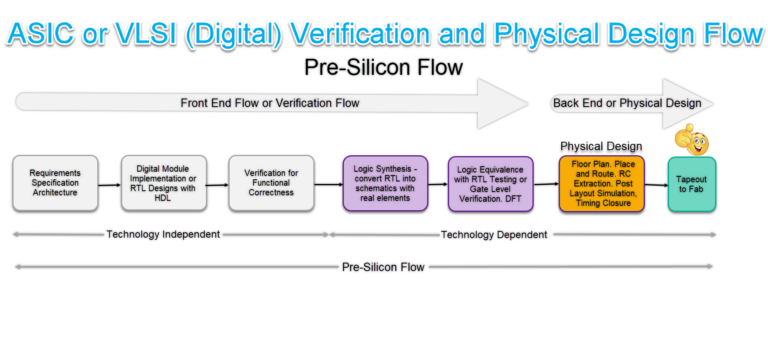

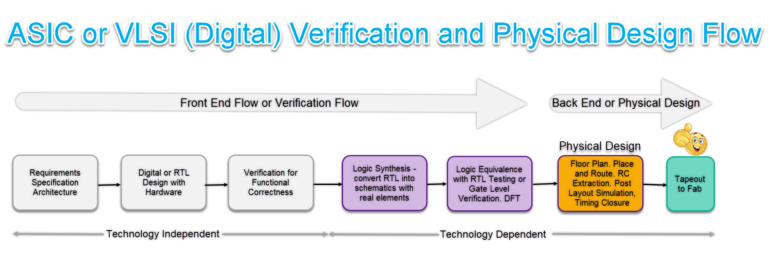

Abstract This article provides an overview of Register Transfer Level (RTL) Design, Verification and Synthesis Flow. In simple term, this is called VLSI/ASIC Verification Flow or the Frontend Design of the the VLSI Flow. It describes the fundamentals of RTL design and the process of RTL design. The article will also discuss RTL synthesis, RTL for synchronous and…

VLSI Design Steps & Designers Choice of EDA Tools VLSI Design Steps and Designers Choice of EDA Tools in Each Step of ASIC Design Flow – VLSI Verification & Physical Design Flow or Pre-Silicon Flow of Digital VLSI/ASIC These are the top EDA tools or the Top Preferences of the VLSI Designers in Each Step…

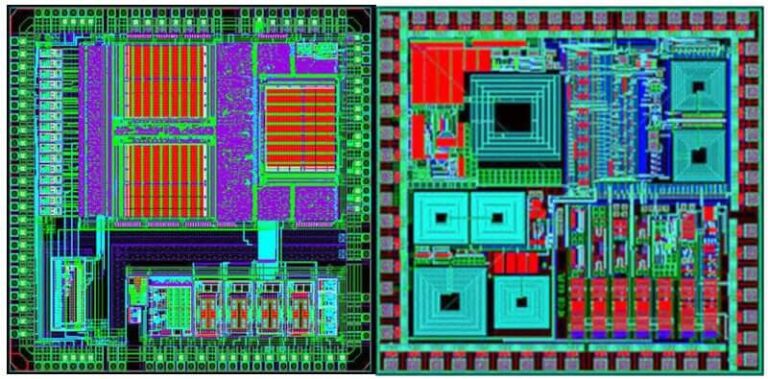

ASIC or Digital VLSI Design and Verification Flow Contents 1. What is an ASIC 2. Chip Design Flow 3. Requirements 3. Specifications 4. Architecture 4. Digital Design 5. Verification 6. Logic Synthesis 7. Logic Equivalence 8. Placement and Routing 9. Validation VLSI stands for Very Large Scale Integration, which is a technology used to create…

Real Number Modeling with System Verilog – Course Duration Real Number Modeling – 3 Days (8 hours per Day) Real Number Modeling with System Verilog – Abstracts Nowadays, the semiconductor industry directs its attention to mixed-signal System-on-Chip (SoC) applications. Main targets are the creation of accurate and fast mixed-signal SoC designs, composed of both digital…

Length of the Webinar: 3 Days (8 Hours Per Day) Course Description In this course, you use the Virtuoso® ADE Explorer and Spectre® Circuit Simulator/Spectre Accelerated Parallel Simulator (APS) to simulate analog circuits with Verilog-A models. Verilog-A is a high-level language that uses modules to describe the structure and behavior of analog systems and their…

Become Silicon Synergy Certified Length of the Webinar: 3 Days (8 Hours Per Day) Course Description In this course, you learn Mixed-Signal verification with UVM. The Accellera standard Universal Verification Methodology – Mixed Signal (UVM-MS) architecture is used to develop a mixed-signal testbench and verify the Mixed-Signal Design Under Test (MS-DUT). You get to analyze…

Enroll Today for Free Conference or Webinar on Mixed Signal Design It’s our mission to inform and stimulate how-to discussions on the hottest topics in our training catalog. Training and Webinars are delivered live by subject matter experts either on-line or visiting your colleges. At the end of each Training/Webinar, we host an open Q&A…

VLSI(IC) Design Cycle VLSI(IC) Design Flow: The process of designing, manufacturing, and testing ICs is complex and exhaustive. The main contributors are the design and verification teams, IP vendors, and IC manufacturers. This article introduces the integrated circuit (IC) design cycle. It is intended for people who have recently joined the semiconductor/EDA industry. I couldn’t…

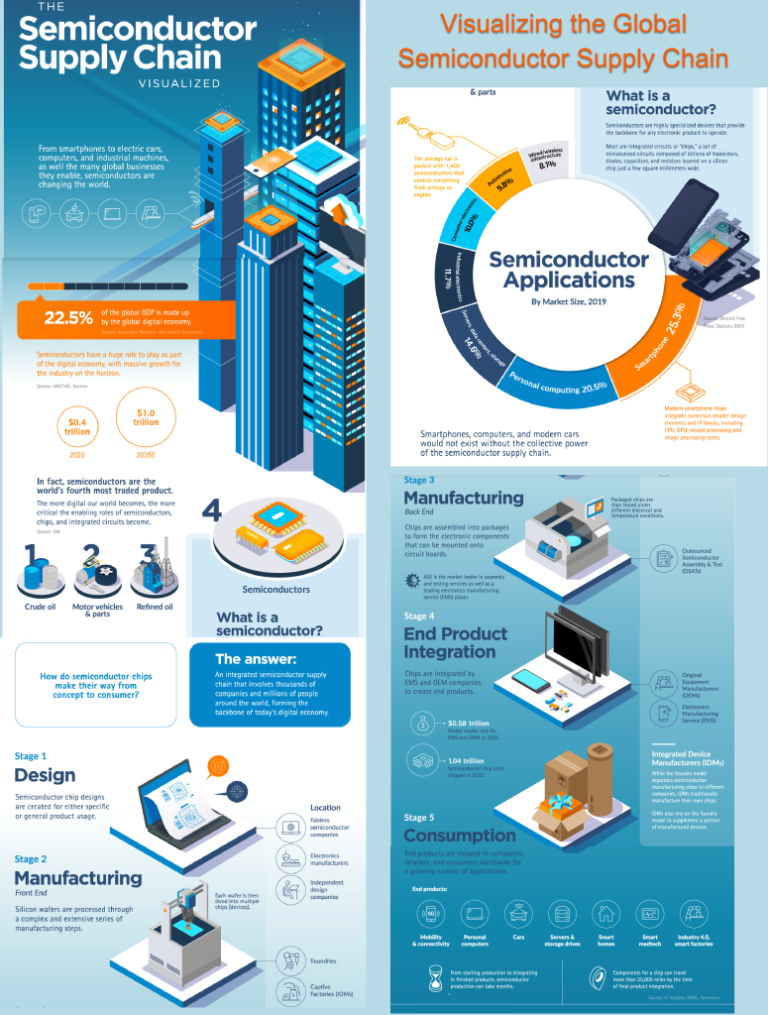

Our digitally-driven society is powered by an extremely robust semiconductor supply chain, and until the COVID-19 pandemic, not many people thought about it. But a sudden surge in demand for digital goods, improved technologies, and recovering economies put the strain and spotlight directly on semiconductors. The millions of digital devices we use, from smartphones to…

Physical Design and Verification Our Physical Design and Verification course mainly focused on giving complete hands on experience to physical design or the layout part and physical verification training flow including floor planning with latest tools and full lab practices. By end of the course your will learn to work in Linux environment to use…

Digital IC Design and Verification Digital IC Design and Verification course is designed by 35+ years experienced US industry experts, mainly for fresh engineering graduates and professionals to meet the current and future demands of the semiconductor industry. Our course offers comprehensive RTL Design & Verification Training in Bangalore. RTL design is a crucial step…